銅ハイブリッドボンディング技術における革新的なブレークスルー:3D ICと先端パッケージングのキーテクノロジー

陳冠能 教授、劉昱論

國立陽明交通大學 電子研究所

-

|

序文 |

3次元集積回路(3D IC)技術は、半導体業界におけるイノベーションを促進する重要な技術として、徐々にその地位を確立しつつあります。人工知能(AI)、高性能コンピューティング(HPC)、5G通信、モノのインターネット(IoT)といったアプリケーションの発展に伴い、従来のムーアの法則(Moore’s Law)は飽和状態に達し、平面微細化による性能向上は物理的な限界に直面しています。3D ICは、複数のチップやウェハを垂直方向に積層することでこの限界を打破し、より高い演算性能、より低い消費電力、そしてより緊密なシステム統合を実現します。従来の2D ICと比較して、3D ICはチップ間の接続距離を大幅に短縮し、寄生抵抗と寄生容量を大幅に低減できるため、信号伝送速度の向上、電力損失の低減、そして全体的な帯域幅の拡大を実現し、高帯域幅メモリ(HBM)、AIアクセラレータ、データセンターなどのアプリケーションに最適な選択肢となっています。さらに、3D IC技術は異種集積化も促進し、異なるプロセスノード、異なる材料、さらには異なる機能を持つコンポーネントを単一パッケージで連携させることを可能にします。例えば、プロセッサ(CPU/GPU)、メモリ(DRAM)、RF、センサーなどの異種チップをコンパクトなパッケージに統合することができ、システムパフォーマンスが向上するだけでなく、コストが最適化され、設計の柔軟性が向上します[1]、[2]。

より高いコンピューティング性能、より低いレイテンシ、よりエネルギー効率の高い電子部品に対する需要が高まるにつれて、半導体業界は3D IC技術へと急速に移行しています。消費電力の低減と入出力(I/O)密度の向上のニーズにより、集積回路(IC)相互接続技術は継続的に進化しています。従来のフリップチップ(Flip-chip)技術では、高性能チップとパッケージ間の標準的な相互接続としてはんだバンプ(Solder bumps)を利用しており、そのピッチは通常100 µmを超えています[1]。ただし、この大ピッチのはんだバンプ相互接続では、寄生抵抗と寄生容量の影響があり、信号減衰とエネルギー消費の増加につながり、信号の整合性と電力効率にさらに影響を及ぼし、最終的にはシステム全体のパフォーマンスを制限します[3]。集積密度を高め、高帯域幅メモリ(HBM)スタッキングやその他の高度なパッケージングアプリケーションを可能にするために、業界ではピッチが10~50µmのマイクロバンプ(Microbump)技術に注目しています。しかし、依然としてマイクロバンプは、エレクトロマイグレーション(Electromigration, EM)、接触抵抗の増加、アンダーフィル(Underfill)による信頼性の問題など、相互接続技術のさらなる微細化を妨げている根本的な課題に直面しています[4]。

これらの課題に対処するため、ハイブリッドボンディング技術(Hybrid bonding)が画期的なソリューションとして登場しました。この技術は、10µm以下のピッチでCu-Cu接合(Cu-to-Cu bonding)および誘電体-誘電体接合(Dielectric-to-dielectric bonding)を直接実現できるため、はんだが不要になり、相互接続の寄生効果が大幅に低減し、シグナルインテグリティと電力効率が大幅に向上します[5]、[6]。最近のW2W(Wafer to Wafer)およびD2W(Die to Wafer)ハイブリッドボンディング技術の進歩により、相互接続ピッチはサブミクロンレベルにまで縮小されました。これは高密度の3Dシステムオンチップ(3D-SoC)アーキテクチャの実現に不可欠であり、人工知能(AI)アクセラレータ、データセンターアーキテクチャ、高度なモバイルプロセッサなど、高帯域幅、低遅延のデータ伝送を必要とするアプリケーションにも拡張できます[7]、[8]。さらに、ハイブリッドボンディングの優れた熱的・機械的安定性により、異種材料の統合が促進され、異なる材料や機能部品をコンパクトで高性能なシステムアーキテクチャにシームレスに統合することが可能になります[9]。

|

開発の軌跡 |

ハイブリッドボンディングは、チップ、ウェハ、基板などの、金属材料と周囲の誘電体材料からなる2つの構造を積層するために用いられます。ハイブリッドボンディングプロセスでは、金属材料と誘電体材料は別々に接合されます。ハイブリッドボンディングは現在、3D IC集積化における究極の技術の一つとされていますが、ハイブリッドボンディングが開発される以前の、最も初期の3D IC集積化技術はCu-Cu接合技術から始まりました。1999年から2002年にかけて、マサチューセッツ工科大学(MIT)のReifの研究チームは、図1に示すように、キャリアウェハ(Siキャリア)、研磨技術(Thinning Technology)、Cu-Cuの直接接合を含むウェハレベル3D集積化方式を提案しました[1]。ウェハ内の部品への熱損傷を避けるため、Cu-Cu接合の最高温度はCMOSプロセスのサーマルバジェットに合うように400℃に制限されました。2001年、Reifのチームの陳冠能教授は、Cu-Cu接合が400℃で正常に実行でき、接合界面が完全に消失することを実証し、この技術の実現可能性を証明しました[10]。図2に示すように、熱圧着接合条件は400℃、400mbarで30分間、その後窒素(N₂)雰囲気中で400℃、30分間のアニール処理でした[11]。この400℃の接合温度は、その後のハイブリッドボンディングプロセスにも用いられました。

図1 3D ICの例 [1] |

図2 接合30分後のCu-Cu接合層[10] |

2000年から2005年にかけて、陳冠能教授は、Cu-Cu接合に関する多数の研究を発表し、その内容には形態の変化、接合強度、接合パラメータ基準、および電気的特性が含まれていました[11-14]。試験結果によると、良好なCu-Cu接合構造の平均接触抵抗は約1×10⁻⁸ Ω−cm²であり、最小では1.2×10⁻9 Ω−cm²に達することがあります[14]。IBMに在籍時の2006年、陳冠能教授は主要な国際半導体会議であるIEDMで、構造設計とパターン形成の両方を考慮したCu-Cu接合に関する包括的な研究を発表しました[15]。しかしながら、Cu-Cu接合方式では、銅の周囲に他の材料がないため、銅の腐食や全体的な接合強度不足などの潜在的な信頼性の問題につながる可能性があります。これらの問題は、銅接合界面の隙間をアンダーフィルで埋めることで解決できますが、銅パッドの高さがわずか数ミクロンであるため、この方法は非常に困難です。さらに、アンダーフィル法はチップレベル接合にのみ適用可能であり、ウェハレベル接合には使用できません。

これらの問題を解決するために、研究者たちは直感的な解決策を提案しました。それは、Cu-Cu接合の前に周囲に誘電体材料を追加するというものです。適切な誘電体材料としては、二酸化ケイ素(SiO₂)やポリマー材料などが挙げられます。理想的な接合シナリオは、Cu-Cu、誘電体-誘電体の接合を同時に実現することです。2005年にRPIのGutmannとLuのチームは、図3に示すように、10,000Nの圧力で250℃、30分間加熱した後、さらに350℃で30分間加熱するという、200mmウェハレベルのCu/BCB(benzocyclobutene, ベンゾシクロブテン)熱間圧着技術を実証しました[16]。この技術は同年、”Hybrid Bonding”(ハイブリッドボンディング)と正式に命名されました[17]。それ以来、研究者たちはCu/ポリマーおよびCu/SiO₂構造に基づく理想的なハイブリッドボンディング技術の開発に取り組んできました。ポリマーの柔性(compliance)を活用するため、IBMの科学者たちは”Lock and key”ハイブリッドボンディング構造を開発しました。この構造では、上面ウェハの銅パッド/銅ピラー構造が「錠」として機能し、下面ウェハのポリマー(ポリイミドなど)には銅パッド/銅ピラー構造を収容するための「鍵」として機能する大きな穴が設けられています。図4に示すように、この300mmウェハレベルの接合方式は既に実証されており、接合と研磨後のウェハはタングステン貫通シリコンビア(W TSV)を使って外部に接続されています[18]。。

図3 Cu/BCBハイブリッドボンディングの最初の実証 [16] |

図4 Lock-and-Key技術を用いたCu/ポリマーハイブリッドボンディングの実証 [18] |

|

図5 Cu/SiO₂ハイブリッドボンディングの模式図[20] |

IBMの研究経験と成果を基に、国立陽明交通大学に着任後、陳冠能教授はIBMの元同僚と共同で、「Lock and key」方式に基づく300mmウェハレベルのCu/SiO₂ハイブリッドボンディングを実証し、信頼性試験を完了しました[19]、[20]。図5に示すように、熱圧着接合条件は400℃、1時間、2×10⁻⁴torrの真空環境下で10,000Nの圧力をかけました。 |

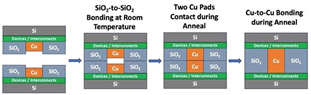

ホットプレスによるCu/SiO₂ハイブリッドボンディングを検討する場合、最も理想的なアプローチは、ダマシン(damascene)法で埋め込まれた銅と、隣接する二酸化ケイ素誘電体材料を直接接合媒体として使用することです。しかし、ダマシンプロセスの特性上、銅パッドのサイズに応じて、銅表面に通常最大50nmの深さの凹部が形成されます。例えば、図6では、銅表面は二酸化ケイ素表面から約20nm下にあります[21]。このような小さな凹部であっても、銅接合の表面形態は不良になります。これは、より硬い二酸化ケイ素表面が最初に接触し、銅パッド中央部での接触を妨げるためです。そのため、ダマシン構造に基づくハイブリッドボンディングの開発は大きな課題となっており、この問題は約20年前から提起されています。興味深いことに、ダマシン銅の独自の特性は、研究者による別のハイブリッドボンディング技術、「ダイレクトボンドインターコネクト(Direct Bond Interconnect, DBI)」の開発を促しました。DBIは当初「ハイブリッドボンディング」という用語を使用していませんでしたが、その中核となる概念は同じです。まず、銅パッドが凹状に形成され、周囲を二酸化ケイ素で囲まれた2枚のウェハまたはチップを室温で酸化物同士の接合によって接合します。その後、銅と銅の接合温度(例えば400℃)でのアニール処理中に、銅の熱膨張係数(CTE)が二酸化ケイ素よりも大きいため、銅の凹部が埋められ、最終的に図7に示すように、銅パッドの拡大接触と接合が形成されます[22]。

この方法は、Cu-Cu接合の際に圧力を加えたり真空環境を利用したりする必要がないため、大量生産に適している可能性があるという点が特筆に値します。さらに、酸化物同士の接合は室温で完了するため、熱圧着接合と比較してプロセス時間が大幅に短縮され、生産能力が向上します。

図6 Cu/SiO₂ 表面形態 [13] |

図7 DBIに基づくハイブリッドボンディングプロセスの概略図 |

|

図8 ハイブリッドボンディングを用いた積層CIS断面の模式図 [22] |

|

|

現在の技術的成果と状況 |

他の業界の取り組みと同様に、imecの研究チームもハイブリッドボンディング技術の開発に積極的に取り組んでいます。imecは従来の材料とは異なるシリコン炭窒化物(SiCN)を誘電体材料として使用しています。SiCNは、表面粗さが非常に小さく(CMP後わずか0.1nm)、SiCN間の接合エネルギーが非常に高いため、バックエンドオブライン(BEOL)配線で広く使用されている材料です。最近、imecのE.Beyneのチームは、図9に示すように、ピッチ400nm、銅パッドサイズがわずか200nmのウェハレベルハイブリッドボンディングを実証しました[23]。これらのファインピッチハイブリッドボンディングの成果は、3D ICによる高密度相互接続の実現可能性を示しています。

図9 400nmピッチハイブリッドボンディング相互接続 [23] |

接合温度は応力、反り、デバイス性能に密接に関連しているため、400℃の接合温度はCMOSのサーマルバジェットと一致しているものの、より低温の接合技術の開発が依然として重要な課題となっています。銅同士の接合には通常、300~400℃の高温が必要です。その主な理由は、銅表面に酸化物層があるためで、この酸化物層は、2枚の基板からの銅原子の相互拡散を妨げるため、十分な温度を与えて銅原子の拡散と粒成長を促進し、接合を実現する必要があります。これに対して、陳冠能教授の研究チームは、金属パッシベーション層(Metal passivation layer)を使用した低温銅同士の接合技術の実証に成功しました。銅表面に非常に薄い(約10nm)金属パッシベーション層を堆積することで、銅の酸化を効果的に防ぐことができます(図10参照)[24]。

この技術では、特定の金属をパッシベーション層として使用すると、接合プロセス中に銅原子が薄いパッシベーション層の粒界を拡散して接合界面に到達する傾向があります。このとき、2枚の基板の銅原子は酸化の影響を受けないため、接合構造を正常に形成できます。この現象は、金、銀、パラジウム、チタンなどの特定の金属でのみ発生することは注目に値します。さらに、この研究では、銅原子の拡散経路は主にパッシベーション層の粒界を通過し、パッシベーション層の厚さと表面粗さが接合の成功に影響を与える重要な要因であることも示されました。このCu-Cu接合プラットフォームでは、パッシベーション層の厚さと表面粗さを適切に制御することにより、室温に近い接合温度40℃を達成することに成功しており、その後のアニールによって接合強度を高めることができます[25]。一般に、金属パッシベーションに基づくCu-Cu接合技術は、W2WおよびC2W(Chip to Wafer)スケールの両方で実証されており、接合温度は150℃以下に抑えることができます。図11に示すように、金属パッシベーション層を介したCu/SiO₂ハイブリッドボンディング技術は、優れた信頼性を示すだけでなく、優れた電気特性も備えています[26]。可能な限り低い接合温度を達成できることに加えて、さらに重要なのは、金属パッシベーション層は薄い金属膜による表面保護の原理に基づいており、銅材料の結晶粒径や配向を意図的に変化させないため、その応用において寸法収縮による制約を受けないことです。

図10 金属パッシベーション層のCu-Cu接合の模式図 [24] |

図11 さまざまな金属パッシベーション層を備えたCu/SiO2ハイブリッドボンディング [21] |

|

今後の動向と結論 |

ハイブリッドボンディングは、高性能コンピューティング(HPC)や高帯域幅メモリ(HBM)の技術ノードによく使用されるため、高歩留まり・高信頼性を実現するマルチウェハスタックが標準要件となるでしょう。しかし、スタックには複数の薄型ウェハが含まれ、ハイブリッドボンディングプロセスは高温を伴うため、接合システムに大きな応力と反り(warpage)が生じ、後続のプロセスやパッケージングに影響を及ぼす可能性があります。そのため、低温ハイブリッドボンディング技術の開発は重要な課題です。さらに、適切なハイブリッドボンディング材料(特に誘電体材料)の選択も、適切な接合方法(DBIやTCBなど)を決定する上で重要です。例えば、SiCNはハイブリッドボンディングに効果的に適用されており、接合温度と処理時間を低減するためのさまざまなポリマー材料も提案されています。さらに、業界では低温接合を実現するために、銅に代わる材料の検討も進められています。最後に、高精度なハイブリッドボンディング装置は、接合結果を確実に成功させるための重要な要素であることは間違いありません。極めて粉塵の少ない接合環境が求められることに加え、接合プロセス中の表面状態とパーティクル制御は、接合装置の性能に大きく依存します。さらに、ハイブリッドボンディングにおける銅パッド間隔とサイズ制御には、アライメント精度(alignment accuracy)が極めて重要です。将来のロジックおよびメモリ積層アプリケーションでは、相互接続密度の向上に伴い、サブミクロンレベルのアライメント誤差制御が基本要件となっています。そのため、ハイブリッドボンディング装置の精度と性能は極めて重要です。

ハイブリッドボンディング技術は、過去20年間で3D ICと先端パッケージングにおいて飛躍的な進歩を遂げてきました。Cu-Cu接合やDBI接合の開発に伴い、この技術はW2WおよびC2Wプロセスで広く利用され、継続的な技術革新を推進してきました。ハイブリッドボンディングは、システムの小型化、性能、効率の限界を押し広げ続けています。低温ハイブリッドボンディングやファインピッチ相互接続などの主要技術の開発により多くの課題が解決され、先進的な半導体システムの厳しい要件を満たしてきました。今後は、材料開発、接合装置およびCMP装置の改良、そして新しい接合方法の登場が、残された課題を克服する上で重要な役割を果たすと期待されます。これには、コスト削減、歩留まり向上、反り低減、マルチウェハ積層応力の管理などが含まれます。これらの重要な課題が解決されることで、ハイブリッドボンディング技術は高密度、低消費電力、高信頼性の半導体デバイスの発展において、今後ますます重要な役割を果たすことになるでしょう。

Reference:

[1] R. Reif, A. Fan, Kuan-Neng Chen, and S. Das, "Fabrication technologies for three-dimensional integrated circuits," Proceedings International Symposium on Quality Electronic Design, San Jose, CA, USA, 2002, pp. 33-37, doi: 10.1109/ISQED.2002.996687.

[2] V. Chidambaram et al., “Dielectric Materials Characterization for Hybrid Bonding,” Proc. IEEE 71st Electronic Components and Technology Conference (ECTC), 2021, pp. 426-428. DOI: 10.1109/ECTC32696.2021.00078.

[3] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, "Microstructure Evolution and Abnormal Grain Growth During Copper Wafer Bonding," Applied Physics Letters, vol. 81, no. 20, pp. 3774-3776, 2002.

[4] T. Fukushima, T. Tanaka, and M. Koyanagi, "Three-Dimensional Integration Technology with Through-Silicon Vias and Microbumps," Japanese Journal of Applied Physics, vol. 47, no. 4S, pp. 2801-2808, Apr. 2008.

[5] C. S. Tan, K. N. Chen, and S. J. Koester, "Wafer-Level 3-D Integration Technology," IEEE Transactions on Electron Devices, vol. 55, no. 3, pp. 1003-1010, Mar. 2008.

[6] K. N. Chen, "Advances in Low-Temperature Cu-to-Cu Direct Bonding," IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 7, no. 4, pp. 557-567, Apr. 2017.

[7] B. Zhang, F. Niklaus, G. Stemme, and E. Beyne, "Scaling Cu/SiCN Wafer-to-Wafer Hybrid Bonding Down to 400 nm Interconnect Pitch," IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 2024, pp. 312-318.

[8] M. Motoyoshi, "Through-Silicon Via (TSV)," Proceedings of the IEEE, vol. 97, no. 1, pp. 43-48, Jan. 2009.

[9] E. Beyne, "3D System Integration: Hybrid Bonding and Beyond," IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 2019, pp. 676-679.

[10] Kuan-Neng Chen, Andy Fan, and Rafael Reif, "Microstructure Examination of Copper Wafer Bonding," Journal of Electronic Materials, 30, pp 331- 335, 2001.

[11] K. N. Chen, A. Fan, C. S. Tan and R. Reif, “Microstructure evolution and abnormal grain growth during copper wafer bonding,” Applied Physics Letters, 81(20), pp 3774-3776, 2002.

[12] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, “Temperature and Duration Effect on Microstructure Evolution during Copper Wafer Bonding”, Journal of Electronic Materials, 32(12), pp 1371-1374, 2003.

[13] K. N. Chen, C. S. Tan, A. Fan and R. Reif, "Morphology and bond strength of copper wafer bonding", Electrochemical and Solid-State Letters, 7(1), pp G14- G16, 2004.

[14] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, “Contact Resistance Measurement of Bonded Copper Interconnects for Three-Dimensional Integration Technology”, IEEE Electron Devices Letters, 25(1), pp 10-12, 2004.

[15] Kuan-Neng Chen, Sang Hwui Lee, Paul S. Andry, Cornelia K. Tsang, Anna W. Topol, Yu-Ming Lin, JianQiang Lu, Albert M.Young, Meikei Ieong, and Wilfried Haensch, “Structure Design and Process Control for Cu Bonded Interconnects in 3D Integrated Circuits”, 2006 International Electron Devices Meeting (IEDM), pp. 367-370, San Francisco CA, Dec. 11-13, 2006.

[16] J. J. McMahon, J.-Q. Lu and R. J. Gutmann, "Wafer bonding of damascene-patterned metal/adhesive redistribution layers for via-first three-dimensional (3D) interconnect," Proceedings Electronic Components and Technology, 2005. ECTC '05., Lake Buena Vista, FL, USA, 2005, pp. 331-336 Vol. 1, doi: 10.1109/ECTC.2005.1441287.

[17] R.J. Gutmann, J.J. McMahon, S. Rao, F. Niklaus, and J.- Q. Lu, “Wafer-Level Via-First 3D Integration with Hybrid-Bonding of Cu/BCB Redistribution Layers”, Proceedings of International Wafer-Level Packaging Congress (IWLPC), pp. 122-127, SMTA, Nov. 2-4, 2005.

[18] R. R. Yu, F. Liu, R. J. Polastre, K.-N. Chen, X. H. Liu, L. Shi, E. D. Perfecto, N. R. Klymko, M. S. Chace, T. M. Shaw, D. Dimilia, E. R. Kinser, A. M. Young, S. Purushothaman, S. J. Koester and W. Haensch, “Reliability of a 300-mm-compatible 3DI technology based on hybrid Cu-adhesive wafer bonding”, 2009 Symposia on VLSI Technology and Circuits, Kyoto, Japan, Jun. 15-18, 2009.

[19] K. N. Chen, T. M. Shaw, C. Cabral, Jr., and G. Zuo, “Reliability and structural design of a wafer-level 3D integration scheme with W TSVs based on Cu-oxide hybrid wafer bonding”, 2010 International Electron Devices Meeting (IEDM), San Francisco CA, Dec. 6-8, 2010.

[20] Kuan-Neng Chen, Zheng Xu, and Jiang-Qiang Lu, “Electrical Performance and Alignment Investigation of Wafer-level Cu-oxide Hybrid Bonding,” IEEE Electron Device Letters, 32(8), pp. 1119-1121, Aug 2011.

[21] K.N. Chen, C.K. Tsang, A.W. Topol, S.H. Lee, B.K. Furman, D.L. Rath, J.-Q. Lu, A.M. Young, S. Purushothaman, and W. Haensch, “Improved Manufacturability of Cu Bond Pads and Implementation of Seal Design in 3D Integrated Circuits and Packages”, 23rd International VLSI Multilevel Interconnection (VMIC) Conference, Fremont CA, Sep.25-28, 2006.

[22] Y. Kagawa et al., "An Advanced CuCu Hybrid Bonding For Novel Stacked CMOS Image Sensor," 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, Japan, 2018, pp. 65-67, doi: 10.1109/EDTM.2018.8421453.

[23] B. Zhang et al., "Scaling Cu/SiCN Wafer-to-Wafer Hybrid Bonding down to 400 nm interconnect pitch," 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 2024, pp. 312- 318, doi: 10.1109/ECTC51529.2024.00058.

[24] Yan-Pin Huang, Yu-San Chien, Ruoh-Ning Tzeng, and Kuan-Neng Chen, “Demonstration and Electrical Performance of Cu–Cu Bonding at 150 °C With Pd Passivation,” IEEE Transactions on Electron Devices, 62(8), pp. 2587-2592, Aug. 2015.

[25] Zhong-Jie Hong, Demin Liu, Shu-Ting Hsieh, Han-Wen Hu, Ming-Wei Weng, Chih-I Cho, Jui-Han Liu, and Kuan-Neng Chen, “Room Temperature Cu-Cu Direct Bonding Using Wetting/Passivation Scheme for 3D Integration and Packaging,” 2022 Symposia on VLSI Technology and Circuits, Honolulu, HI, Jun. 12-17, 2022.

[26] Demin Liu, Po-Chi Chen, Chien-Kang Hsiung, Shin-Yi Huang, Yan-Pin Huang, Steven Verhaverbeke, Glen Mori, and Kuan-Neng Chen, “Low Temperature Cu/SiO2 Hybrid Bonding with Metal Passivation,” 2020 Symposia on VLSI Technology and Circuits, Virtual Conference, Jun. 14-19, 2020.