|

序言 |

铁电材料是一类很特殊的极性化合物,基于自发电极化效应,可表现出优良的铁电、压电、热电、以及非线性光学等特性,因此,在数据存储、红外光感测、超声波、光电微波通讯等领域,皆有许多重要应用。铁电内存是具有潜力可突破 von Neumann 架构瓶颈、实现「储存级内存」与「内存内计算」的下世代内存主流技术之一,近几年随着材料研究的重大进展而受到关注,成为半导体产业争相竞逐的新热点。

过去由于钙钛矿材料的铁电性 (Ferroelectricity) 在薄膜厚度低于某个临界值之后会急遽劣化,使得记忆胞尺寸难以持续缩微,进而导致内存密度无法有效提高,因此早期铁电内存的产品应用,仅局限于特定利基市场。而近几年随着半导体相容材料二氧化铪 (HfO2) 被发现具有铁电相特性,且该材料工艺整合难度低、成本上也具有优势,才终于为铁电内存开展另一波新的产业契机。HfO2 是半导体领域相当熟悉的材料,长久以来被广泛应用于 28nm 以下 CMOS 的高 K 介电层,以及 DRAM 电容中的介电质。HfO2 必须掺杂特定元素杂质之后,才会产生出铁电特性。

反铁电性 (Antiferroelectricity) 是材料物理性质的一种,它与铁电性密切相关。无论具有铁电性或反铁电性,都归属铁电材料的应用范畴。近期的研究发现,通过调整 HfO2 中添加 Si 的比例,可制作出具有反铁电特性的薄膜。而将锆 (Zr) 掺杂于 HfO2 中,也能够改变其铁电特性。随着 Zr 的掺杂比例越高,介电效果会随之变大。当 Zr 掺杂比例高于铪 (Hf) 时,该氧化铪锆 (HfZrO2; HZO) 化合物的电滞曲线,将会由铁电性转变为反铁电性。

根据研究结果显示,采用反铁电 HZO 材料的内存,具有优于原 HfO2 铁电内存的耐久力 (Endurance) ,且具更快的切换速度、更小的操作偏压、与更轻微的唤醒效应 (Wake-up) 等组件特性表现。在其 HZO 材料加上偏压后,会产生残余极化量,适合用来制作挥发性内存。而经由调整电极的功函数差 (Work-function Difference)、反铁电层内部氧空穴 (Oxygen Vacancy)、或是固定电荷层与接口偶极子 (Interface Dipole) 创造出内建电场 (Built-in E-field) 等特殊的工艺或结构处理后,可使原先于双极性操作下对称的 P-V 特性偏移导致不对称,使其在偏压为 0V 时也具有优异的残余极化量、可用以制作非挥发性内存。此外,采用 3D NAND 架构的反铁电穿隧结面内存,也可实现稳定多阶位 (Multilevel Cell, MLC) 的高密度记忆储存功能。基于如此宽广多样的应用可能性,已使得反铁电 HZO 成为下世代铁电内存材料的首选。

|

闳康科技于本期特别邀请半导体先进材料及组件研究领域顶尖学者 李敏鸿教授,为「科技新航道 | 合作专栏」撰文,介绍反铁电材料于内存的技术应用及未来发展趋势,与读者分享此一重要科技领域的学术研究进展。 |

|

闳康科技研发中心处长 陈弘仁 2023/2/5

极具潜力的新兴内存材料!反铁电氧化铪锆

台湾师范大学 光电工程研究所

李敏鸿教授

研究生:向国瑜、罗肇丰、曾涵桢、张福生、李志贤、芮玮成、张以太

(本篇由李敏鸿教授提供、闳康科技修编)

-

铁电 (Ferroelectric) 材料现今已有诸多研究[1]-[5],且目前有相当多研究其于内存的应用,而与铁电相似却又具特殊性的反铁电 (Anti-Ferroelectric),亦为铁电材料之一,近年来,因铁电铪基氧化物 (Hf-Based Oxide) 蓬勃发展,相关研究论文于此材料的反铁电特性也有进展,本文将就材料科学、铁电工程、及操作手法方面切入,针对反铁电特性适材所用,开发相对应的应用。

|

反铁电材料的历史 |

|

2020 年为发现铁电材料的 100 周年,1920 年 Valasek 于罗谢尔盐 (Rochelle Salt) 发现铁电性[6],二战期间,美国、苏俄及日本科学家寻找用介电质材料,来替代云母于电容的应用,在钙钛矿 BaTiO3 中发现铁电效应。有关反铁电特性的文献,早自 1950 年的东京工业大学 G. Shirane 教授及 E. Sawagachi 教授,就已发表反铁电钙钛矿 PbZrO3[7]-[9],而贝尔实验室的 C. Kittel 于 1951 年提出理论,证明反铁电存在[10]。图一为固态材料反铁电历史的发展时程[16]。

1953 年,钙钛矿 PbHfO3 的反铁电相已被确认[11],同时,英国利兹大学 (University of Leeds) 的 L.E. Cross 及 B.J. Nicholson 研究 NaNbO3 晶体,并显示出双迟滞曲线[12],利用 BaTiO3 铁电材料的 Devonshire 模型,及 Kittel 论文的学说,并解释 NaNbO3 的双迟滞曲线[13];1959 年,W. Cochran 说明了位移相变的理论[14];在基础研究方面,美国 B. Jaffe、W.R. Cook、H. Jaffe 于 1960 年代初期开发的 PbZrO3-PbTiO3 (PZT),引起人们对反铁电与铁电边界的兴趣,利用PZT 相图量测反铁电相变的参数[15]。2007 年,奇梦达 (Qimonda AG) 在硅掺杂的氧化铪 (Si:HfO2) 中发现铁电特性,并于 2011 年[17]及 2012 年[18],分别发表氧化铪 (HfO2) 中掺杂硅 (Si) 与锆 (Zr),依掺杂量不同可具有铁电及反铁电特性,展开与目前半导体兼容工艺的铁电铪基氧化物 (Hf-Based Oxide) 蓬勃发展的铁电与反铁电研究。 |

图1 固态材料的反铁电材料发展史[1]。 |

|

反铁电材料的特性 |

因具有丰富的科学性,以及在高能领域的实用性,而备受关注。反铁电是材料内部两个相邻单晶的极性平行、反向排列的电偶极子 (Dipole),而两者重新构成一个新的晶格,给予足够强大的外加电场,可使电场相反方向的相位发生反转成同极性的铁电相,进而观察到双迟滞曲线。在外加电场为零时,晶格内两种反向且平行的极性相互抵消;相反地,若外加电场无法将其翻转,说明反铁电材料具大于该外加电场的抗性。

图2 (a) 为顺电 (Paraelectric)、铁电与反铁电的相变状态示意图;图2 (b) 为反铁电材料所量测到典型的 (Typical) 反铁特性磁滞曲线[5,6]。在低极化状态时,当偏压增加至矫顽场 EF 后,极化量急剧上升。而在反转场方向时,P-E 电滞曲线沿着另一个矫顽场 EA (< EF),以另一个路径急剧减小,到线性区之前形成另一回路。

图2 (a) PbZrO3 中,顺电、铁电 与反铁电 的示意图;(b) Pb0.98La0.02 (Zr0.66Ti0.10Sn0.24) 0.995O3 典型双电滞曲线[8]。 |

|

反铁电钙钛矿 (Perovskite) 材料 |

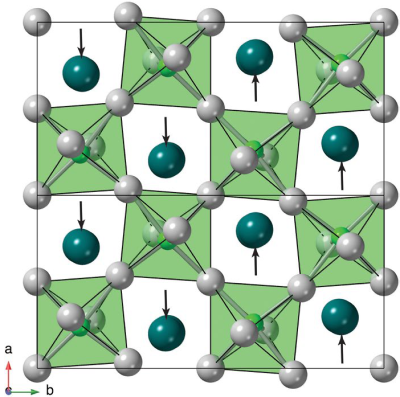

在铪基氧化物之前,最为熟知的铁电材料大部分属于钙钛矿材料。而在 ABO3 钙钛矿的结构中,A 离子占据立方晶格八个角的位置如图3,氧原子则占据立方晶格六个面的中心位置、共同组成面心立方结构,最后 B 离子再占据立方晶格的中心位置,形成 BO6 八面体结构。A 阳离子为稀土族离子、B 阳离子为 Al3+、O2- 为阴离子。图4为 PbZrO3 钙钛矿结构[19],其中,深绿色原子为 Pb、浅绿色为 Zr、灰色为 O,箭头为 Pb 位移,显示为反铁晶体管结构图,不对称相是影响反铁电的重要因素。早期研究铁电应用,多使用钙钛矿材料,但部份元素却具有毒性,考虑到环境污染及热预算的问题,目前 CMOS 工艺有使用上的限制。

图3 ABO3 钙钛矿铁电材料结构图。 |

图4 PbZrO3 的晶体结构 (Pb:深绿色原子,Zr:浅绿色,O:灰色)。显示 PbZrO3 的基本反铁电结构,其中箭头表示离子位移引起相变[19]。 |

|

反铁电二维材料 (2D Material) |

|

二维材料为新的光电材料,根据层数和成分的不同,可分为像超导体、金属、半导体和绝缘体等各种特性[20]。 |

近年来,具有铁电或反铁电相的二维材料 CuBiP2Se6 已被广为尝试。如图5 (a) 所示,在 AgBiP2Se6 中,硫化物骨架具有由 Ag(Bi) 和 P-P 对填充的八面体空隙。块状晶体 Ag+ 和 Bi3+ 位置显示出类似反铁电的排序[21]。凡得瓦力交互作用将相邻层黏合在一起,凡得瓦键的弱点使材料可以剥离成二维层。详细密度泛函理论 (DFT) 研究指出,离子和凡得瓦交互作用平衡,可以控制这些材料的铁电和反铁电排序[20]。图5 (b) 为 β-In2Se3 中的偶极子在使用 ADF-STEM (环形暗场扫描穿透式电子显微镜) 射影、测得原子的位移,并观察到边界。

图5 (a) 将 CuBiP2Se6 的晶体结构中 Ag 和 Bi 位置显示,呈现类似反铁电体的排序;(b) 在 β-In2Se3 中的原子位移[20]。 |

|

氧化铪系统的铁电与反铁电 |

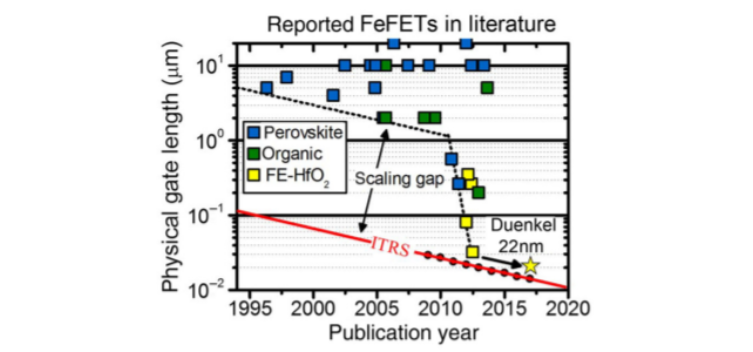

早期研究铁电应用,多为使用钙钛矿材料,例如:锆钛酸铅 (PbZrTiO3, PZT)、钛酸钡 (BaTiO3, BTO)、钽酸锶铋 (SrBi2Ta2O9, SBT)、钛酸锶 (SrTiO3, STO) 等。但由于钙钛矿型铁电材料的部分元素具有毒性,且面临微缩问题如图6 [22],因此需找寻解决方法。奇梦达于 2007 年发现,于铪氧化物掺杂硅 (Si:HfO2) 会具有铁电特性。后续各界也陆续发表,于铪基氧化物中掺杂硅、铝 (Al)、钆 (Gd)、锶 (Sr)、镧 (La)、锆 (Zr) 元素,皆会具有铁电特性如图7 [23];2011 年,T. S. Böscke 提出氧化铪系统的铁电相为正交晶相 (Orthorhombic Phase),此晶相的形成是从四方晶相 (Tetragonal Phase) 冷却过程中转变而来,图8为其示意图[17]。

|

图6 国际半导体技术发展蓝图与铁电层厚度比较[22]。 |

图7 氧化铪系统掺杂各元素的电滞曲线特性[22]。 |

|

图8 四方晶相转变为正交晶相,以及不同铁电相的极化状态示意图[17]。 |

|

反铁电氧化铪硅 (Si:HfO2) |

| 通过调整氧化铪中硅 (Si) 的比例,可以得到具有反铁电现象的薄膜[17],从图9可以发现,低掺杂 HfO2 的薄膜表现出正铁电,而随着 SiO2 的掺杂浓度逐渐上升,电滞曲线(黑色)和电容(粗红色),会随着 SiO2 混合物增加而改变,最后可得掺杂 5.6 mol. % 的薄膜电滞曲线,从铁电转变为反铁电。 |  图9 不同 SiO2 掺杂浓度的电容与电滞曲线[17]。 |

|

反铁电氧化铪锆(Hf1-xZrxO2) |

| J. Müller 团队于 2012 年发表—若将 Zr 掺杂于 HfO2 中[23],Zr 占据 HfO2 中掺杂比例的多寡,将影响铁电特性。文献中使用原子层沉积系统 (Atomic Layer Deposition, ALD),来更准确地控制 Hf 与 Zr 的比例,使其调整至优化、以利于铁电特性的研究。图10(a) 为随着 Zr 掺杂比例由低至高的电滞曲线,和介电值对电场的关系图,Zr 掺杂比例越高,介电值随之变大;Zr 掺杂的比例高于 Hf 时,电滞曲线由正铁电特性变化至反铁电特性。 |  图10 不同Zr比例的极化量和介电常数对电场关系图[23]。 |

|

反铁电氧化铪锆—高耐力 (Endurance) 及高速操作 (High-Speed Switching) 特性 |

|

氧化铪锆与目前半导体工艺兼容、且具可微缩的优势,故于未来的新兴内存,为可期待的材料,而使用于电子组件时,因具有高耐力、快速反应的电性表现,应用时可针对此优势加以利用,如类DRAM (DRAM-Like) 操作组件。 |

|

如图11所示,铁电电容大约于 2x105 次时严重衰退,而反铁电电容则是 1x109 次循环后,仍可正常操作[24]。因铁电氧化铪锆在应力及适当退火条件下,会形成正交晶系 (Orthorhombic System),其操作至衰退机制中,因氧空穴陷 (Oxygen Vacancy) 游移至可转动的偶极子造成钉住[25],会形成非铁电相的单斜晶系 (Monoclinic System) [26],进而造成失效层 (Dead Layer),故整体残余极化量下降;反铁电中晶体具四方晶系 (Tetragonal System),因相变步骤及可独立正负极性相域 (Domain) [27]的特性,表现出天生具有高耐力的特点。

在快速反应的特性中,极化-操作频率量测如图12 (a) 与 (b) [28],在反铁电电容中,最大极化量Ps变化的程度远小于铁电电容,到 1MHz 时都可反应。由于高频率中铁电层偶极子的翻转速度,无法跟上其电压变换的速度,反铁电的偶极子的翻转时间常数 (τ0) 较短之故,可由从 Nucleation Limited Switching (NLS) 模型推论[29],其架构如图13所示。 |

图11 正铁电电容与反铁电电容耐力比较[24]。

图12 不同频率下饱和极化量:(a) 铁电电容与 (b) 反铁电电容[28]。

|

图13 根据 NLS 模型所建构出的模拟架构[29]。 |

|

于铁电模型中加入回转场 (Back-Switching Field, EBS) 以套成反铁模型,并以实验数据校正,计算出铁电与反铁电时间常数分别为1203ns与223ns,如图14 (a) 与 (b) 所示,此常数直接影响了极化方向转变的速度,因此跟随着频率增加,反铁电比起正铁电响应速度更快[28]。 |

图14 不同频率下仿真铁电电容的P-V特性:(a) 铁电电容与 (b) 反铁电电容[28]。 |

|

反铁电氧化铪锆虽具有高耐力及高速切换能力,但于内存使用上有所限制,接下来将从材料科学面向出发,进而以铁电工程改质,从应用面AFE-RAM、AFE-FTJ及AFE-FET的优化操作方案切入研究。 |

|

反铁电随机存取内存 (Anti-Ferroelectric Random-Access-Memory, AFE-RAM) |

由于反铁电电容的极化量对电压 (Polarization-Voltage, P-V) 特性与铁电电容具有极大的差异,图15(a) 为典型铁电电容与反铁电电容,于双极性操作下的 P-V 特性图[30],其中偏压为 0V 时,铁电电容具有明显且优异的残余极化量,适合作为非挥发性内存 (Nonvolatile-Memory),反铁电电容则显示微弱的残余极化量,不适合作为非挥发性内存,与铁电材料相比,具有更优异的耐力度、较小的操作偏压与轻微的唤醒效应 (Wake-Up),接者将说明反铁电于随机存取内存的应用。

反铁电电容 P-V 特性如同两个对称的铁电极化循环,分别于正与负极性区域,图15(b) 施加偏压为正极性区域 (0V to 3V) 的单极性操作,其中铁电电容失去原本于双极性操作下的铁电特性,而反铁电电容于单极性偏压下,仍然保持良好的铁电特性,此单极性操作方法虽然降低操作电压,但是需要额外施加一个固定偏压于反铁电电容,故反铁电电容适合应用于挥发性内存。

图15 铁电电容与反铁电电容的 P-V 特性操作于 (a) 双极性与 (b) 单极性区域。 |

| 借由调整电极的功函数差 (Work-Function Difference) [31]、反铁电层内部氧空穴[32]、固定电荷层与界面偶极子 (Interface Dipole) [33]创造内建电场 (Built-in E-Field),使原先于双极性操作下对称的 P-V 特性偏移导致不对称,而此不对称的反铁电 P-V 特性,于偏压为 0V 时,具有优异的残余极化量,适合作为非挥发性内存如图16 (a),其中图16 (b) 与 (c) 的反铁电电容的非挥发极化特性,分别为 RuOx 与 TiN 电极的功函数差、反铁电层内部氧空穴数量约 1018 cm-3 与氧化铝层的固定电荷,以及氧化铝层与反铁电层接口的偶极子。 |  图16 (a) 内建电场使反铁电的 P-V 偏移导致不对称;(b) 反铁电电容的非挥发极化特性分别为 RuOx 与 TiN 电极的功函数差、反铁电层内部氧空穴数量约 1018 cm-3 与 (c) 氧化铝层的固定电荷以及氧化铝层与反铁电层接口的偶极子[31][33]。 |

目前文献中,英特尔 (Intel) 曾发表,借由 RuOx 与 TiN 电极的功函数差及 3D 数组结构,来达到超高密度嵌入式动态随机存取内存 (Embedded Dynamic Random-Access Memory, eDRAM) 技术,如图17 (a)、图17 (b) 显示,材料的内电场及偶极子缺陷会影响极化量,图17 (c) 则显示,不同内电场会有功函数差异、造成极化量的差异,导致内存窗口 (Memory Window, MW) 的不同。

图17 (a) 3D 数组结构 eDRAM 的 TEM 截面图;(b) 为内电场及偶极子缺陷对极化量的影响;(c) 为功函数差和 MW 关系图[32]。 |

|

反铁电穿隧式结面 (Anti-Ferroelectric Tunneling Junction, AFTJ/AFE-FTJ) 内存 |

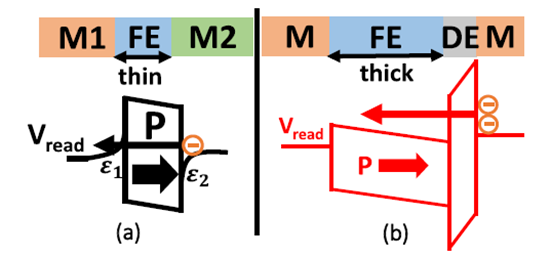

铁电穿隧式结面 (Ferroelectric Tunnel Junction, FTJ) 内存基本上是个电阻式的两端组件,如图18,有单层铁电结构、或双层的铁电与介电结构两种,单层铁电结构由两层金属中间夹着一层铁电薄膜,所组成金属 / 铁电层 / 金属 (Metal/Ferroelectric Layer/Metal, MFM),其中利用两端电极材料所造成的屏蔽长度 (Screening Length) 不同、产生势垒 (Barrier Height) 差,进而开 (On) 与关 (Off) 穿隧电流 (Funneling Current) 调变。双层的铁电与介电结构,是两层金属中间夹一层铁电薄膜层、一层介电层,所组成 金属 / 铁电层 / 介电层 / 金属 ( Metal / Ferroelectric Layer / Dielectric Layer / Metal, MIFM) 双层铁电穿隧结面组件,其原理是透过不同极化方向时,铁电层势垒高度的不同,导致穿隧具有不同的穿隧电阻 (Tunnel Electro-Resistance, TER)。

FTJ 具备低阻态 (Low-Resistance State, LRS) 及高组态 (High-Resistance State, HRS),以此原理能在 FTJ 区分出 0 与 1 的内存储存能力,其中单层与双层 FTJ 两者结构的差异,会造成电子穿隧长度明显不同,单层 FTJ 的电子只需穿隧铁电层,而双层 FTJ 的电子穿隧介电层形成开电流,其关电流则需穿隧铁电层与介电层,如图19 (a) [35]。2019 年,德国 Technical University of Dresden 的 B. Max 团队,发表 12nm HZO 搭配 1nm Al2O3 作为双层 FTJ 结构[35],操作电压 (Set Voltage) 与开关电流相关性如图19(b),借由改变写入和抹除的电压,调控铁电层的极化量,借此调整穿隧势垒,进而调变穿隧电流值的高低。

|

图18 (a) 单层铁电穿隧结面组件结构及 (b) 双层铁电穿隧结面组件结构能带图[34]。 |

图19 (a) 双层 FTJ 的开关状态能带图;(b) 操作电压对于开电流以及关电流的依赖性,不同操作电压下,以 2V 读取的电流值[35]。 |

反铁电中,可由前文提及的方法创造内建电场,使反铁电于偏压为 0V 时,具有残余极化量如图14 (a),且为能提升记忆密度,图20 (a) 为 3D 与非门 (NAND) 与阶梯型 (Minimal incremental Layer Cost, MiLC) 的架构,为可将内存单位面积超越 4F2 嵌入式非挥发性内存 (embedded Non-Volatile Memory, eNVM) 的策略之一,3D NAND 架构的反铁电穿隧结面内存的截面 (Cross-Sectional) 穿透式电子显微镜 (Transmission Electron Microscope, TEM) 如图20 (b) 与 (c),图20 (d) 与 (e) 透过快速傅利叶转换 (Fast-Fourier Transformation, FFT) 影像与 X 射线能量散布分析仪 (Energy-Dispersive X-ray Spectroscopy, EDS) 分析,证明此反铁电氧化铪锆具有优异的结晶质量、与相关元素位置的正确性,其中 3D 垂直型反铁电穿隧结面的 I-V 特性,显示于 1V 具有优异的电流比 (Ion/Ioff ratio) > 100x 如图20 (f) [36]。

图21(a) 与 (b) 分别显示双层的铁电及反铁电穿隧结面的电流比特性,于搭配 Al2O3 厚度 0 nm 至 4 nm,而反铁电穿隧结面搭配 Al2O3 厚度 2 nm 至 4 nm的电流比皆~100x,可见反铁电经工程上的调变后,其在穿隧式结面存储元件有比铁电更佳的表现,另外,反铁电穿隧结面搭配 Al2O3 厚度 2 nm 具有最小操作偏压,图21 (c) 与 (d) 为透过逐渐增强写入电压,来展示反铁电穿隧结面搭配 Al2O3 厚度2 nm,具有优异的多阶位 (Multi-Level Cell, MLC) 特性、与线性对称且稳定的深度学习特性[36]。

图20 (a) 3D NAND 与阶梯型架构;(b) 与 (c) 为3D NAND 架构的反铁电穿隧结面组件的 TEM 截面图;(d) 与 (e) 为快速傅利叶转换影像与 EDS 分析;(f) 3D vertical FTJ 的 I-V 特性显示于 1V 具有优异的电流比 (Ion/Ioff ratio) > 100x[36]。 |

图21 (a) 与 (b) 分别显示双层的铁电及反铁电穿隧结面的电流比特性于搭配 Al2O3 厚度 0 nm 至 4 nm;(c) 与 (d) 为透过逐渐增强写入电压,来展示反铁电穿隧结面搭配 Al2O3 厚度 2 nm,具有优异的多阶位特性与深度学习特性[36]。 |

|

反铁电场效晶体管 (Anti-Ferroelectric Field-Effect-Transistor, AFE-FET) |

|

将铁电材料制作于晶体管栅极堆栈,完成铁晶体管已是多数研究单位目前研发重点,但因反铁电于 0V (Standby) 时无残余极化量,故欲达成反铁电场效晶体管,便需铁电工程予以达成。 |

2018 年,东京大学小林正治 (Masaharu Kobayashi) 教授团队[37]成功验证,将反铁电材料应用于场效晶体管,在场效晶体管的栅极上加一个反铁电电容,并调控面积比,电容与栅极面积比为 1:32,成功制做出有记忆窗的场效应晶体管,如图22。2019 年,罗彻斯特理工学院 (Rochester Institute of Technology) 的 Kai Ni 教授团队[38],提出利用多层正铁或单层反铁电材料,达成多峰矫顽场 (Multi-Peak Ec) 的概念,以达到稳定多阶记忆,并利用仿真展示此概念,如图23,达成多峰矫顽场的 P-V loop,与其记忆机率分布。

|

图22 场效晶体管的栅极上加一个反铁电电容,并调控面积比,电容与栅极面积比为 1:32,成功制做出记忆窗[37]。 |

图23 多峰矫顽场可以应用于多阶内存(N 个铁电层可以存储 N 阶)[38]。 |

单一反铁电层达成多阶操作在 2022 年[39]实验验证其可行,使用介于类反铁电的单层氧化铪锆的铁电-反铁电场效应晶体管 (AFE-FE-FET),如图24 (a) 和 (b) 所示。使用类反铁电的氧化铪锆,拥有 0V 具有残余极化量优势,以及多峰矫顽场特性,AFE-FE-FET 达到超低写入 / 擦除电压 (|VP/E| = ±4 V),以多峰矫顽电场概念,制做出稳定的多阶操作,如图25,其耐力 >105 次与优异的数据保持能力 (Data Retention),在 65°C 时 >104 秒。

|

图24 正铁电、类反铁、反铁电的 (a) P-V 图与 (b) I-V 图[39]。 |

图25 (a) AFE-FE-FET 和 FE-FET 的示意图;(b) MLC 操作的脉冲波形图 (c) AFE FE-FET 和 (d) FE-FET 的 MLC ID-VG [39]。 |

|

结论 |

经由本文对应用端的组件细部讨论,可知反铁电于内存的应用,原本难以达成非挥发性储存,但因其具有优异的耐力、轻微唤醒及快速反应等特点,可于工程上经过调整,并针对其用途加以改良,故其中的材料科学就显得相对重要。针对反铁电特性适材所用,开发相对应的材料分析手法,如晶相分析、极化晶域判断、氧空穴分布等,都是未来可开发的领域。

|

闳康编辑室后记 |

自 1920 年,美国学者 Joseph Valasek 首度发表罗谢尔盐具有自发电极化效应的研究结果,迄今已超过百年。由于罗谢尔盐机械强度低、且易吸水潮解,使得当时铁电现象的发现仅具象征性科学意义。不过基于铁电物理性质的独特性,及其广阔应用前景,仍吸引了无数研究人员投入,积极寻找其它更有应用潜力的铁电新材料。因此,有长达半世纪的时间,全世界皆聚焦于钙钛矿 (Perovskite) 铁电材料的基础研究,而开发出 BaTiO3 (BTO) 与 Pb[ZrxTi1-x]O3 (PZT),两款具有强稳铁电特性的经典材料,使得铁电材料在军事及商业方面的应用成为可能。尤其 BaTiO3 具有特别简单的结构组成,其为研究铁电相变中的晶体结构变化提供了方便的参考模型,也使得学者 A. F. Devonshire 在 1949 年时,据以建立了预测铁电现象的唯象理论(将铁电材料的自由能,描述为两极化态之间存在一能垒的双阱势),该理论对于理解铁电体的特性,与加速铁电材料研究进展,至今依然扮演极为重要的角色。

大致来说,铁电材料的常见应用,主要是利用它们的压电性、热电性、电光效应以及高介电特性。基本上,所有的铁电材料几乎都同时具备铁电性 (Ferroelectricity) 和压电性 (Piezoelectricity)。

铁电性是指在一定温度范围内,材料会产生自发的极化。由于铁电体晶格中的正负电荷中心不重合,即使没有外加电场时,也能产生一电偶极矩,并且此自发极化可以在外电场作用下改变方向。当温度高于某一临界值时,铁电材料的晶格结构会发生改变、正负电荷中心重合,使得该自发极化现象消失,此一温度临界值称为居里温度 (Curie Temperature, Tc)。

压电性是实现机械能与电能相互转换的一种性质。若在某一方向上对材料施加外力,使其发生形变,该材料内部会发生极化、并在表面产生电荷,此称为压电效应。相反的,若是对该材料施加电场,将使其发生形变而产生机械力,此则称为逆压电效应。另外,也有某些特殊的多铁性铁电材料,例如 BiFeO3,在光辐照下,材料内部会激发出非平衡载流子,使得电子云结构发生不对称变化,从而诱导出宏观极化,而产生许多特殊的物理现象,如反常光伏效应、光折变效应等。

近年来由于人工智能、物联网、5G 通讯及智能车载等新兴科技崛起,带来了大量信息的实时分析需求,既有的高容量存储组件例如 DRAM 及 NAND Flash,在耗电量及数据访问速度上,已无法满足未来的科技应用。并且,随着半导体工艺线宽缩微已超越 14nm、晶体管技术主流迁移到 FinFET 或 GAA 等先进结构,长期应用于 CMOS 芯片的嵌入式存储单元 NOR Flash,也已无法跟上 SoC 整合工艺的发展需求,必须要有全新的嵌入式非挥发性内存技术,才能搭配下一世代先进工艺所制造的 ASIC 和 MCU。

铁电内存是一款基于自发电极化原理的电容式组件,不仅有可靠的非挥发性、格外快速的读写速度、反复存取的高耐用性及超低耗电量等特点,其在工艺复杂度和成本考虑上也具有极大优势,是最有机会成为后摩尔定律时代的新兴储存解决方案。

早在 1950 年代后期,学者即以钙钛矿铁电材料 BTO,发展出第一个 FeFET 内存。该组件在工艺上十分简单,仅需将制作于 MOSFET 晶体管的栅极介电层,改以铁电材料取代即可。然而,根据第一原理计算预估,由于钙钛矿材料的铁电性,在薄膜厚度低于临界值约 6 个单晶格之后,即会急遽劣化,限制了内存密度、无法持续提高,因此早期产品的应用,仅局限于特定利基市场。自从 2011 年德国学者发现掺杂的二氧化铪具有良好铁电性质,该材料便开始受到关注、并被迅速导入铁电内存的应用开发。

HfO₂是一种具有宽能隙和高介电常数的陶瓷材料,近年来被广泛应用于半导体先进工艺中,替代 SiO₂ 作为 MOSFET 的栅极绝缘层,以解决该组件缩微的尺寸极限问题。相较于传统的钙钛矿铁电材料,HfO2 主要优点不仅在于材料可完全兼容于半导体工艺,更重要的是,即使在 10 nm 的厚度下,HfO2 薄膜依然仍能保有铁电性。此外,它的居礼温度高达 470°K,在室温下运作也不成问题。

HfO2 必须在掺杂其它元素后、在特殊的晶相时,才会显示出铁电性质。目前学界研究经常使用的掺杂物包括 Si、Y、Sr、La、Ge、N 等,它的晶相主要包括单斜相 (Monoclinic)、四方相 (Tetragonal) 和斜方相 (Orthorhombic) 三种,其中以单斜相能量最低,但是只有斜方相者有所需的铁电性质。如何以适当的掺杂元素及其比例、接口物质、与退火条件等,使 HfO2 形成稳定的铁电材料,目前还是研究中的课题。不过,选择 HfO2 作为铁电内存材料,已显示出极大的市场应用潜力。

无论是铁电性或反铁电性,都是属于铁电材料的应用领域。铁电性的形成,主要是在一些电介质晶体中,晶胞的结构使正负电荷中心不重合,而出现电偶极矩,产生不等于零的电极化强度,使晶体具有自发极化。通常,铁电体自发极化的方向不相同,但在一个小区域内,各晶胞的自发极化方向相同者,这个小区域就称为铁电畴 (Ferroelectric Domains)、两畴之间的界壁称为畴壁。

铁电畴的极化方向和强度各不相同,在整个材料中随机分布、相互抵消,整体的铁电材料并没有极化的现象产生。对铁电材料施加电场后,每个铁电畴的极化方向会趋于一致,并达到饱和极化值 (Saturation Polarization)。当外加电场超过正的矫顽电场 (Positive Coercive Field) ,或低于负的矫顽电场 (Negative Coercive Field),即可改变铁电材料的电偶极方向。而当该外加电场移除之后,铁电材料内仍会存在剩余的极化量 (Remanent Polarization)。因此,本质上铁电内存非常适合应用于制作非挥发内存组件。

所谓反铁电性,是材料内部两个相邻单晶的极性平行、反向排列的电偶极子 (Dipole),两者重新构成一个新的晶胞。在外加电场为零时,晶格内两种反向且平行的极性相互抵消,使宏观上自发极化强度为零。当给予足够强大的外加电场,可以使电场相反方向的极性相位发生反转,形成相同极性的铁电相,进而观察到与铁电性材料类似的双电滞曲线。但是当电场减小回复为零时,曲线在到线性区之前,会形成另一闭回路,因此无剩余的极化量存在。

反铁电性是材料的一种特性,包括温度、压力、外部电场、生长方法等参数变化影响,都可能令其增强或减弱。特别的是,在某一足够高的温度下,反铁电性也会消失。目前所使用的反铁电性材料,大多是采用 HfO2 中掺杂 Zr 制作而成,称之为氧化铪锆。随着 Zr 的掺杂比例增高,HZO 的介电值会随之变大。当 Zr 掺杂比例高过 Hf 时,该 HZO 的电滞曲线,将会由铁电性转变为反铁电性。

根据近期研究结果,反铁电性材料通常比铁电性材料具更优异的耐久度、更快的切换速度、更小的操作偏压、与更轻微的唤醒效应等。此外,反铁电内存经过适当的工艺或结构改善处理后,可同时适用于制作挥发性内存、非挥发性内存、或实现多阶位的高密度记忆储存功能。2022 年时,日本东京大学已利用反铁电材料,代替原铁电性材料的铁电栅极绝缘体,成功开发出一款 3D 垂直场效应晶体管,验证了 3D 堆栈存储概念。该研究成果已在 2022 IEEE 硅奈米电子研讨会中发表,未来很有机会用于生产尺寸更小、耗电更低的超高密度内存组件。

附带一提,除了应用于内存之外,反铁电二维材料也可作为新的光电材料,根据层数和成份的不同,展现类似超导体、金属、半导体和绝缘体的多样特性,也可应用于传统 MOSFET 上,提供其可提高栅极氧化物的介电性能,即所谓「负电容」效应。使用负电容铁电材料制作栅极层,会导致电流相对于原栅极电压增加得更快,从而降低晶体管的亚阈值摆幅 (Subthreshold Swing)。亚阈值摆幅是衡量晶体管开启与关断状态之间,相互转换速率的性能指针,它代表源漏电流变化 10 倍所需栅电压的变化量,又称为 S 因子。S 值越小,意味着开启关断速率 ON/OFF 越快。

2019 年年底,国际电子组件会议 (International Electron Device Meeting, IEDM) 首度将铁电内存主题列为一单独的新议程「Sec 15: Memory Technology-Ferroelectric」,此举明确揭示了产学界对于铁电内存技术研发新动向的关注。再者,就铁电内存近期最令人振奋的研究成果,是其在存储耐久性上似已获得大跃进。特别是发现「在铁电 HfO2 内掺杂 La 元素,可使内存存储次数提升至 1011 次以上」之后,此已经直逼 DRAM 的耐久性了。而比利时研究机构 IMEC 也于 2022 年 IEDM 会议上,展示了一款掺杂 La 的反铁电 HZO 电容器。其不仅循环操作次数可达 1011 次,并拥有更良好的电滞曲线及更轻微的唤醒效应。该反铁电电容技术同时具备了高性能、微尺寸、及半导体工艺兼容性,未来应有机会成为实现新一代嵌入式或独立式铁电随机存取内存 (FeRAM) 技术的关键。另外,2019 年时,普渡大学利用半导体兼容铁电材料 α-In2Se3,成功将晶体管与所谓的「铁电随机存取存储器 (Ferroelectric RAM)」结合起来,实现了兼具讯息计算处理与存储功能的新型铁电半导体场效应晶体管架构,并在知名期刊《自然电子学 (Nature Electronics)》上发表。

随着全球越来越多研究团队的投入开发,铁电内存的未来架构雏型已初略成形。以前受限于所用铁电材料特性的限制,应用只局限于利基市场。而随着越来越多例如HfO2及HZO等的新颖铁电材料研究迈入成熟,相信必然很快能为铁电内存推升另一波新的产业发展契机。本篇文章针对「反」铁电内存的材料及技术应用发展,提供了全面性介绍,可有效帮助读者快速地学习、了解此最具市场潜力的先进技术。李敏鸿教授的研究专长主要包括前瞻晶体管、高功率组件、以及太阳能电池等领域。他早期于台湾大学取得博士学位后,曾先后在工研院的电子所 (ERSO) 及影像显示科技中心 (DTC) 服务长达数年,累积了丰富的产学研发经验。而自 2007 年起,李教授即在台湾师范大学任教、致力于学术研究至今,已发表的期刊論文超过 150 篇,并拥有数篇重要的发明专利。2019 年时获选为 IEEE Senior Member。

李教授及其研究团队对于提升先进半导体领域的核心技术优势,具有极大的贡献。闳康科技非常荣幸今年度可以和李教授携手进行产学合作,提供该团队在铁电随机存取内存工艺研究上所需的完整分析服务。闳康科技拥有完备的检测设备与专业技术经验,能全面满足先进半导体组件在工艺、封装及失效分析方面的各种分析检测需求。

References:

[1]V. A. Isupov, “Ferroelectric and antiferroelectric perovskites Pb (B′0.5B′′0.5) O3.” Ferroelectrics, vol. 289, no. 1, pp. 131-195., 2003.

[2]G. A. Smolenskii, V. A. Bokov, V. A Isupov, N. N. Kraini, P. E Pasynkov, and A. I. Sokolov, “Ferroelectrics and related materials.” New York: Gordon and Breach, 1984.

[3]K. M. Rabe, “Antiferroelectricity in oxides: A reexamination” Functional metal oxides: new science and novel applications, pp. 221-244., 2013.

[4]X. Tan, C. Ma, J. Frederick, S. Beckman, and K. G. Webber “The Antiferroelectric ↔ Ferroelectric Phase Transition in Lead-Containing and Lead-Free Perovskite Ceramics” Journal of the American Ceramic Society, vol. 94, no. 12 pp. 4091-4107.,2011.

[5]T. Mitsui, “Ferroelectrics and Antiferroelectric” Springer Handbook of Materials Data, pp. 901-934., 2018.

[6]J. Valasek, “Piezo-Electric and Allied Phenomena in Rochelle Salt” vol. 17, no. 4, pp. 475, 1921.

[7]G. Shirane, E. Sawaguchi, and Y. Takagi, “Dielectric Properties of Lead Zirconate” Physical Review, vol. 84, no. 3, pp. 476, 1951.

[8]G. Shirane, “Ferroelectricity and Antiferroelectricity in Ceramic PbZrO3 Containing Ba or Sr.” Physical Review, vol. 86, no. 2, pp. 219, 1952.

[9]E. Sawaguchi, H. Maniwa, and S. Hoshino “Antiferroelectric Structure of Lead Zirconate” Physical Review, Vol. 83, no. 5, pp. 1078, 1951.

[10]C. Kittel “Theory of Antiferroelectric Crystals” Physical Review, vol. 82, no. 5, pp. 729., 1951.

[11]G.Shirane, and R. Pepinsky“Phase Transitions in Antiferroelectric PbHfO3” Physical Review, vol. 91, no. 4, pp. 812., 1953.

[12]L.E. Cross, and B.J. Nicholson “LV. The optical and electrical properties of single crystals of sodium niobate” The London, Edinburgh, and Dublin Philosophical Magazine and Journal of Science , vol. 846, no. 376, pp. 453-466, 2009.

[13]L. E. Cross “VII. A thermodynamic treatment of ferroelectricity and antiferroelectricity in pseudo-cubic dielectrics” The Philosophical Magazine: A Journal of Theoretical Experimental and Applied Physics, vol. 1, no. 1, pp. 76-92., 1995.

[14]W. Cochran “Crystal stability and the theory of ferroelectricity” Advances in Physics, vol. 9, no. 36, pp. 387-423, 1960.

[15]H. Jaffe, “Piezoelectric Ceramics” Journal of the American Ceramic Society, vol. 41, no. 11, pp. 494-498, 1958.

[16]C. A. Randall, Z. Fan, I. Reaney, L. Q. Chen, and S. Trolier‐McKinstry , “Antiferroelectric: History, fundamentals, crystal chemistry, crystal structures, size effects, and applications” Journal of the American Ceramic Society,. vol. 104, no. 8, pp. 3775-3810, 2021.

[17]T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger “Ferroelectricity in hafnium oxide thin films” Applied Physics Letters, vol. 99, no. 10, pp. 102903, 1958.

[18]J. Müller, T. S. Böscke, U. Schröder, S. Mueller, D. Bräuhaus, U. Böttger, L. Frey, and T. Mikolajick “Ferroelectricity in Simple Binary ZrO2 and HfO2” Nano letters, vol. 12, no. 8, pp. 4318-4323, 2012.

[19]D. L. Corker, A. M. Glazer, J. Dec, K. Roleder, and R. W. Whatmore“A Re-investigation of the Crystal Structure of the Perovskite PbZrO3 by X-ray and Neutron Diffraction” Acta Crystallographica Section B: Structural Science, vol. 53, no. 1, pp. 135-142, 1997.

[20]J. R. Reimers, S. A. Tawfik and M. J. Ford “van der Waals forces control ferroelectric–antiferroelectric ordering in CuInP2S6 and CuBiP2Se6 laminar materials” Chemical science, vol. 9, no. 39, pp. 7620-7627, 2018.

[21]C. Xu, Y. Chen, X. Cai, A. Meingast, X. Guo, F. Wang, Z. Lin, T. W. Lo, C. Maunders, S. Lazar, N. Wang, D. Lei, Y. Chai, T. Zhai, X. Luo, and Y. Zhu “Two-Dimensional Antiferroelectricity in Nanostripe-Ordered In2Se3” Physical Review Letters, vol. 125, no. 4, pp. 047601, 2020.

[22]M. H. Park et al., "Review and perspective on ferroelectric HfO2-based thin films for memory applications," MRS Communications, vol. 8, no. 3, pp. 795-808, 2018.

[23]J. Muller et al., "Ferroelectricity in simple binary ZrO2 and HfO2," Nano letters, vol. 12, no. 8, pp. 4318-4323, 2012.

[24]Milan Pešic et al., "Comparative Study of Reliability of Ferroelectric and Anti-Ferroelectric Memories" IEEE Trans Device Mater Reliab, VOL. 18, NO. 2, JUNE 2018

[25]M. Pešic´ et al., “Physical mechanisms behind the field-cycling behavior of HfO2-based ferroelectric capacitors,” Adv. Funct. Mater., vol. 26 no. 25, pp. 4601–4612, Jul. 2016, doi: 10.1002/adfm.201600590.

[26]M. Pesic et al., “Root cause of degradation in novel HfO2- based ferroelectric memories,” in Proc. IEEE Int. Rel. Phys. Symp. (IRPS) , Pasadena, CA, USA, 2016, pp. MY-3-1-MY-3-5, doi: 10.1109/IRPS.2016.7574619.

[27]K.-Y. Hsiang, Y.-C. Chen, F.-S. Chang, C.-Y. Lin, C.-Y. Liao, Z.-F. Lou, J.-Y. Lee, W.-C. Ray, Z.-X. Li, C.-C. Wang, H.-C. Tseng, P.-H. Chen, J.-H. Tsai, M. H. Liao, T.-H. Hou, C. W. Liu, P.-T. Huang, P. Su, and M. H. Lee, “Novel Opposite Polarity Cycling Recovery (OPCR) of HfZrO2 Antiferroelectric-RAM with an Access Scheme Toward Unlimited Endurance, ” accepted by Technical Digest, International Electron Device Meeting (IEDM) , San Francisco, Dec. 3-7, 2022.

[28]X. Lyu, M. Si, X. Sun, M. A. Capano, H. Wang and P. D. Ye, "Ferroelectric and Anti-Ferroelectric Hafnium Zirconium Oxide: Scaling Limit, Switching Speed and Record High Polarization Density," 2019 Symposium on VLSI Technology, 2019, pp. T44-T4

[29]Y. Chen, K. Hsiang, Y. Tang, M. -H. Lee and P. Su, "NLS based Modeling and Characterization of Switching Dynamics for Antiferroelectric/Ferroelectric Hafnium Zirconium Oxides," 2021 IEEE International Electron Devices Meeting (IEDM) , 2021, pp. 15.4.1-15.4.4,

[30]K.-Y. Hsiang, C.-Y. Liao, Y.-Y. Lin, Z.-F. Lou, C.-Y. Lin, J.-Y. Lee, F.-S. Chang, Z.-X. Li, H.-C. Tseng, C.-C. Wang, W.-C. Ray, T.-H. Hou, T.-C. Chen, C.-S. Chang, and M. H. Lee, “Correlation between Access Polarization and High Endurance (˜ 1012 cycling) of Ferroelectric and Anti-Ferroelectric HfZrO2,” IEEE International Reliability Physics Symposium (IRPS) , 2022, pp. pp. P9-1-P9-4.

[31]M. Pešić, U. Schroeder, S. Slesazeck, and T. Mikolajick, “Comparative Study of Reliability of Ferroelectric and Anti-Ferroelectric Memories, ” IEEE Transactions on Device and Materials Reliability, vol. 18, no. 2, pp. 154-162, 2018.

[32]S.-C. Chang, N. Haratipour, S. Shivaraman, T. L. Brown-Heft, J. Peck, C.-C. Lin, I.-C. Tung, D. R. Merrill, H. Liu, C.-Y. Lin, F. Hamzaoglu, M. V Metz, I. A Young, J. Kavalieros, and U. E. Avci, "Anti-ferroelectric HfxZr1-xO2 Capacitors for High-density 3-D Embedded-DRAM." IEEE International Electron Devices Meeting (IEDM) , 2020, pp. 28.1.1-28.1.4.

[33]K.-Y. Hsiang, C.-Y. Liao, J.-H. Liu, J.-F. Wang, S.-H. Chiang, S.-H. Chang, F.-C. Hsieh, H. Liang, C.-Y. Lin, Z.-F. Lou, T.-H. Hou, C. W. Liu, and M. H. Lee, “Bilayer-based Antiferroelectric HfZrO2 Tunneling Junction with High Tunneling Electroresistance and Multilevel Nonvolatile Memory,” IEEE Electron Device Letters, vol. 42, no. 10, pp. 1464-1467, 2021.

[34]K. . -Y. Hsiang et al., "Bilayer-Based Antiferroelectric HfZrO2 Tunneling Junction With High Tunneling Electroresistance and Multilevel Nonvolatile Memory," in IEEE Electron Device Letters, vol. 42, no. 10, pp. 1464-1467, Oct. 2021, doi: 10.1109/LED.2021.3107940.

[35]B. Max, M. Hoffmann, S. Slesazeck and T. Mikolajick, "Direct Correlation of Ferroelectric Properties and Memory Characteristics in Ferroelectric Tunnel Junctions," in IEEE Journal of the Electron Devices Society, vol. 7, pp. 1175-1181, 2019, doi: 10.1109/JEDS.2019.2932138.

[36]K. . -Y. Hsiang et al., "Dielectric Layer Design of Bilayer Ferroelectric and Antiferroelectric Tunneling Junctions Toward 3D NAND-Compatible Architecture," in IEEE Electron Device Letters, vol. 43, no. 11, pp. 1850-1853, Nov. 2022, doi: 10.1109/LED.2022.3204445.

[37]Y. Chen et al., "NLS based Modeling and Characterization of Switching Dynamics for Antiferroelectric/Ferroelectric Hafnium Zirconium Oxides," 2021 IEEE International Electron Devices Meeting (IEDM) , 2021, pp. 15.4.1-15.4.4, doi: 10.1109/IEDM19574.2021.9720645

[38]K. Ni et al., "A Novel Ferroelectric Superlattice Based Multi-Level Cell Non-Volatile Memory," 2019 IEEE International Electron Devices Meeting (IEDM) , 2019, pp. 28.8.1-28.8.4, doi: 10.1109/IEDM19573.2019.8993670

[39]C.-Y. Liao et al., “Multipeak coercive electric-field-based multilevel cell nonvolatile memory with antiferroelectric-ferroelectric field-effect transistors (FETs) ,” IEEE Trans. Ultrason., Ferroelectric., Freq. Control, vol. 69, no. 6, pp. 2214‒2221, Jun. 2022.