銅混合接合技術的創新突破:

三維積體電路與先進封裝的關鍵技術

陳冠能 教授、劉昱論

國立陽明交通大學 電子研究所

-

|

前言 |

三維積體電路(3D IC)技術正逐漸成為推動半導體產業創新的關鍵技術,隨著人工智慧(AI)、高效能運算(HPC)、5G通訊和物聯網(IoT)等應用的發展,傳統的摩爾定律(Moore’s Law)已趨於飽和,使得透過平面微縮提升性能的方式面臨物理極限,而3D IC則透過垂直堆疊多個晶片或晶圓來突破這一限制,實現更高的運算效能、更低的功耗以及更緊密的系統整合。與傳統的2D IC相比,3D IC能顯著縮短晶片內部與晶片間的互連距離,大幅降低寄生電阻與寄生電容,進而提升訊號傳輸速度、減少功率損耗並提升整體頻寬,使其成為高頻寬記憶體(HBM)、AI加速器,以及數據中心等應用的理想選擇。此外,3D IC技術還能促進異質整合,使不同製程節點、不同材料甚至不同功能的元件能夠在單一封裝內協同運作,例如將處理器(CPU/GPU)、記憶體(DRAM)、射頻(RF)與感測器(Sensors)等異質晶片整合於一個緊湊的封裝內,不僅提升系統性能,還能優化成本與提升設計彈性 [1], [2]。

隨著對更高運算性能、更低延遲,以及更高能效電子元件的需求不斷增長,半導體產業正快速地邁向三維積體電路技術。為了滿足更低功耗以及更高輸入/輸出(I/O)密度的需求,推動了積體電路(IC)互連技術的不斷演進。傳統上,覆晶(Flip-chip)技術利用錫球(Solder bumps)作為高效能晶片與封裝之間的標準互連方式,其間距通常超過100 µm [1]。然而,這種大間距的錫球互連方式存在寄生電阻與寄生電容效應,導致訊號衰減與能量消耗增加,進一步影響訊號完整性與功耗效率,最終限制整體系統的性能 [3]。為提升整合密度並實現高頻寬記憶體(HBM)堆疊及其它先進封裝應用,業界轉向了微凸塊(Microbump)技術,其間距縮小至10–50 µm。然而,微凸塊仍面臨根本性挑戰,例如電遷移(Electromigration, EM)、接觸電阻增加,以及由底部填充膠(Underfill)引起的可靠度問題,這些問題阻礙了互連技術的進一步微縮 [4]。

為解決這些挑戰,混合接合技術(Hybrid bonding)應運而生,成為突破性的解決方案。該技術能夠在10 µm以下的間距實現直接的銅對銅接合(Cu-to-Cu bonding)與介電材料對介電材料之接合(Dielectric-to-dielectric bonding),消除了對焊錫的需求,大幅降低互連的寄生效應,並顯著提升訊號完整性與功耗效率 [5], [6]。近期在晶圓對晶圓(W2W)與晶片對晶圓(D2W)混合接合技術方面的進展,已將互連間距推進至次微米級(Sub-micron),這對於高密度三維系統單晶片(3D-SoC)架構的實現至關重要,並可進一步拓展於需要高頻寬、低延遲數據傳輸的應用,包括人工智慧(AI)加速器、數據中心架構以及先進的行動處理器 [7], [8]。此外,混合接合優異的熱穩定性與機械穩定性,使其能夠促進異質整合,使不同材料與功能元件能夠無縫地整合於緊湊且高效能的系統架構中 [9]。

|

發展軌跡 |

混合接合可用於堆疊兩個結構,例如晶片、晶圓和基板,每個結構皆由金屬與周圍的介電材料組成,在混合接合過程中,金屬材料和介電材料各自分別進行接合。雖然目前混合接合已被視為3D IC整合的最終技術之一,然而,在混合接合發展之前,最早的3D IC整合技術由銅對銅(Cu-to-Cu)接合技術所開始的。1999年至2002年間,麻省理工學院(MIT)的Reif研究團隊提出了一種晶圓級3D整合方案,其中包括使用載體晶圓(Si carrier)、研磨技術 (Thinning Technology)以及銅對銅直接接合,如圖1所示 [1]。為了避免對晶圓內的元件造成熱損傷,銅對銅接合的最高溫度被限制在400°C,以符合CMOS製程的熱預算。2001年,陳冠能教授在Reif團隊中證明了銅對銅接合可在400°C下成功進行,並且其接合界面完全消失,證明了該技術的可行性 [10]。如圖2所示,其熱壓接合條件為400°C和400 mbar,持續30分鐘,之後在氮氣(N₂)環境下以400°C進行30分鐘的退火 [11]。而此400°C的接合溫度後來持續應用於接續發展的混合接合製程。

圖1. 三維積體電路的範例 [1] |

圖2. 經過 30 分鐘接合後的 Cu-Cu 接合層影像 [10] |

2000年至2005年間,陳冠能教授發表了大量關於銅對銅接合的研究,包括形態演變、接合強度、接合參數準則以及電性特性 [11-14]。測試結果顯示,良好的銅對銅接合結構的平均接觸電阻約為1×10⁻⁸ Ω−cm²,最低可達到1.2×10⁻9 Ω−cm² [14]。2006年,陳冠能教授在IBM工作期間,進一步於國際半導體重要會議IEDM發表了關於銅對銅接合的綜合研究,涵蓋了結構設計和圖案考量 [15]。但在原始的銅對銅接合方案中,銅周圍並無其他材料,有可能導致潛在的可靠性問題,例如銅腐蝕或是整體接合強度不足。雖然這些問題可以使用底部填充膠來填補銅接合界面的間隙,但由於銅墊的高度僅為幾微米,此方法極具挑戰性。此外,底部填充膠的方法僅適用於晶片級接合,而不適用於晶圓級接合。

為了解決這些問題,研究人員提出了一種直覺性的解決方案,即在銅對銅接合前加入周圍的介電材料。適當的介電材料包括二氧化矽(SiO₂)或高分子材料。理想的接合情境是同時實現銅對銅與介電材料對介電材料的接合。2005年,RPI的Gutmann與Lu團隊成功展示了200mm晶圓級Cu/BCB(benzocyclobutene)熱壓接合技術,使用10,000 N的壓力,在250°C下進行30分鐘,隨後升溫至350°C再持續30分鐘,如圖3所示 [16]。該技術在同年被正式命名為「混合接合(Hybrid Bonding)」 [17],自此,研究人員開始發展基於Cu/Polymer (聚合物)和Cu/SiO₂結構的理想混合接合技術。為了利用聚合物的順應性(compliance),IBM科學家開發了一種「鎖與鑰(Lock-and-Key)」混合接合結構,其中頂層晶圓的銅墊/銅柱結構充當「鎖」,而底層晶圓上的聚合物(如聚醯亞胺)則具有較大孔洞,充當「鑰匙」,以容納銅墊/銅柱狀結構。如圖4所示,該300mm晶圓級接合方案已成功展示,並且利用鎢穿矽通孔(W TSV)將接合與研磨後的晶圓導通至外部 [18]。

圖3. Cu/BCB 混合接合的首次展示[16] |

圖4. 採用 Lock-n-Key 技術的Cu/Polymer 混合接合展示 [18] |

|

圖5. Cu/SiO₂ 混合接合示意圖 [20] |

基於IBM的研究經驗與成果,陳冠能教授在加入國立陽明交通大學後與IBM前同事合作,成功展示了基於「鎖與鑰」方案的300mm晶圓級Cu/SiO₂混合接合,並完成了可靠性測試 [19], [20]。如圖5所示,熱壓接合條件為400°C,持續1小時,施加10,000 N壓力,在2×10⁻⁴ torr的真空環境中進行。 |

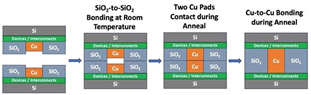

在考慮熱壓Cu/SiO₂混合接合時,最理想的方式是直接使用鑲嵌式(damascene)銅與其旁邊的二氧化矽介電材料作為接合介質。然而,由於鑲嵌製程的特性,銅表面通常會有凹陷,深度可達50 nm,具體數值取決於銅墊尺寸。以圖6為例,銅表面大約低於二氧化矽表面20 nm [21]。即便如此小的凹陷,仍會導致銅接合的表面形貌不佳,因為較硬的二氧化矽表面會先接觸,阻礙銅墊中央的接觸。因此,開發基於鑲嵌式結構的混合接合便成為一個重大挑戰,這個問題大約在20年前就已經被提出。有趣的是,鑲嵌式銅的獨特特性反而促使研究人員開發了另一種混合接合技術,即「直接接合互連(Direct Bond Interconnect, DBI)」。雖然DBI最初並未使用「混合接合」這個術語,但其核心概念是一致的:兩個具有凹陷銅墊且周圍包覆二氧化矽的晶圓或晶片,首先透過氧化物對氧化物(Oxide-to-oxide)接合在室溫下貼合。隨後,在銅對銅接合溫度(如400°C)的退火過程中,由於銅的熱膨脹係數(CTE)大於二氧化矽,會導致銅的凹陷填充,最終形成銅墊的膨脹接觸與接合,如圖7所示 [22]。

值得注意的是,該方法在銅對銅接合時不需要施加壓力或使用真空環境,使其具備量產的潛力。此外,氧化物對氧化物接合可在室溫下完成,與熱壓接合相比,其製程時間大幅縮短,產能也會更高。

圖6. Cu/SiO₂ 表面形貌 [13] |

圖7. 基於 DBI 的混合接合過程示意圖 |

|

圖8. 使用混合接合的堆疊 CIS 橫截面示意圖 [22] |

|

|

目前技術成果與現況 |

如同其他業界的努力,imec研究團隊亦積極開發混合接合技術。與傳統材料不同,imec使用氮化矽碳(SiCN)作為介電材料,氮化矽碳是一種廣泛應用於後段互連(BEOL)的材料,具有極低的表面粗糙度(CMP後僅0.1 nm),且氮化矽碳對氮化矽碳的接合能量極高。近期,imec的E. Beyne團隊成功展示了晶圓級混合接合,間距達400 nm,銅墊尺寸僅為200 nm,如圖9所示 [23]。這些細間距混合接合結果展示了透過三維積體電路整合來實現高密度互連的可能性。

圖 9. 400nm間距混合接合互連 [23] |

由於接合溫度與應力、翹曲以及元件性能密切相關,雖然400°C接合溫度符合CMOS熱預算,但開發更低溫的接合技術仍然是關鍵課題。銅對銅接合通常需要300-400°C的高溫,主要原因在於銅表面存在氧化層,這層氧化物會阻礙來自兩個基板的銅原子的互相擴散。因此,必須提供足夠高的溫度來促進銅原子的擴散與晶粒成長,進而實現接合。陳冠能教授的研究團隊成功展示了一種利用金屬鈍化層(Metal passivation layer)來進行低溫銅對銅接合的技術。透過在銅表面沉積一層極薄(約10 nm)的金屬鈍化層,可以有效防止銅氧化,如圖10所示 [24]。

在此技術中,當使用特定金屬作為鈍化層時,在接合過程中,銅原子會傾向於穿透該薄鈍化層的晶界擴散並到達接合界面。此時,來自兩個基板的銅原子因尚未受到氧化影響,因此能夠順利形成接合結構。值得注意的是,這一現象僅發生於特定金屬,如金、銀、鈀和鈦等。此外,研究還顯示,銅原子擴散的途徑主要透過鈍化層的晶界,而鈍化層的厚度與表面粗糙度是影響接合成功與否的關鍵因素。在此銅對銅接合的平台中,透過適當控制鈍化層的厚度與表面粗糙度,已成功實現接近室溫的40°C接合溫度,並可透過後續退火來增強接合強度 [25]。一般而言,基於金屬鈍化的銅對銅接合技術已在晶圓對晶圓(W2W)與晶片對晶圓(C2W)兩種規模上成功展示,且接合溫度可低於150°C。如圖11所示透過金屬鈍化層的Cu/SiO₂混合接合技術,不僅展現出卓越的可靠性,亦具備良好的電性性能 [26]。除了可以以最低溫的接合溫度實現外,更重要的是,金屬鈍化層其原理來自表面的金屬薄膜保護,並未刻意改變銅材料的晶粒與晶向,因此在應用上將不會受到尺寸微縮的限制。

圖10. 金屬鈍化層之Cu 對 Cu 接合示意圖 [24] |

圖11. Cu/SiO2 混合接合與各種金屬鈍化層 [21] |

|

未來趨勢與結論 |

由於混合接合通常與高效能運算(HPC)及高頻寬記憶體(HBM)技術節點相關,因此具有高良率與高可靠性的多晶片堆疊將成為標準需求。然而,由於堆疊涉及多個薄化晶片,且混合接合過程伴隨溫度升高,會在接合系統中產生顯著應力與翹曲(warpage),進而影響後續製程與封裝。因此,開發低溫混合接合技術是一個關鍵挑戰。此外,選擇適合的混合接合材料(特別是介電材料)對於決定適當的接合方法(如DBI或TCB)也至關重要。例如,SiCN已被成功應用於混合接合,而各種聚合物材料也被提出,以降低接合溫度與加工時間。此外,業界也在探討替代銅的材料,以實現更低溫的接合。最後,一個精密的混合接合設備無疑是確保成功接合結果的關鍵因素。除了需要高度無塵的接合環境外,接合過程中的表面狀況與顆粒控制高度依賴於接合設備的性能。此外,對準精度(alignment accuracy)對於混合接合的銅墊間距與尺寸控制至關重要。在未來的邏輯與記憶體堆疊應用中,由於互連密度的提高,次微米級的對準誤差控制已成為基本需求。因此,混合接合設備的精度與性能至關重要。

過去二十年間,混合接合技術已在三維積體電路與先進封裝領域取得了顯著突破。隨著銅對銅接合與DBI接合的發展,該技術已被廣泛應用於晶圓對晶圓與晶片對晶圓製程,推動了持續的技術創新。混合接合持續突破系統小型化、性能與效率的極限。低溫混合接合與精細間距互連等關鍵技術的發展,已解決許多挑戰,並滿足了先進半導體系統的嚴苛需求。展望未來,材料開發、接合與CMP設備的改進,以及新的接合方法,將在克服剩餘挑戰方面發揮關鍵作用,例如降低成本、提升良率、減少翹曲以及管理多晶片堆疊應力。透過解決這些關鍵問題,混合接合技術將在高密度、低功耗與高可靠性的半導體設備發展中扮演重要角色。

Reference:

[1] R. Reif, A. Fan, Kuan-Neng Chen, and S. Das, "Fabrication technologies for three-dimensional integrated circuits," Proceedings International Symposium on Quality Electronic Design, San Jose, CA, USA, 2002, pp. 33-37, doi: 10.1109/ISQED.2002.996687.

[2] V. Chidambaram et al., “Dielectric Materials Characterization for Hybrid Bonding,” Proc. IEEE 71st Electronic Components and Technology Conference (ECTC), 2021, pp. 426-428. DOI: 10.1109/ECTC32696.2021.00078.

[3] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, "Microstructure Evolution and Abnormal Grain Growth During Copper Wafer Bonding," Applied Physics Letters, vol. 81, no. 20, pp. 3774-3776, 2002.

[4] T. Fukushima, T. Tanaka, and M. Koyanagi, "Three-Dimensional Integration Technology with Through-Silicon Vias and Microbumps," Japanese Journal of Applied Physics, vol. 47, no. 4S, pp. 2801-2808, Apr. 2008.

[5] C. S. Tan, K. N. Chen, and S. J. Koester, "Wafer-Level 3-D Integration Technology," IEEE Transactions on Electron Devices, vol. 55, no. 3, pp. 1003-1010, Mar. 2008.

[6] K. N. Chen, "Advances in Low-Temperature Cu-to-Cu Direct Bonding," IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 7, no. 4, pp. 557-567, Apr. 2017.

[7] B. Zhang, F. Niklaus, G. Stemme, and E. Beyne, "Scaling Cu/SiCN Wafer-to-Wafer Hybrid Bonding Down to 400 nm Interconnect Pitch," IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 2024, pp. 312-318.

[8] M. Motoyoshi, "Through-Silicon Via (TSV)," Proceedings of the IEEE, vol. 97, no. 1, pp. 43-48, Jan. 2009.

[9] E. Beyne, "3D System Integration: Hybrid Bonding and Beyond," IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 2019, pp. 676-679.

[10] Kuan-Neng Chen, Andy Fan, and Rafael Reif, "Microstructure Examination of Copper Wafer Bonding," Journal of Electronic Materials, 30, pp 331- 335, 2001.

[11] K. N. Chen, A. Fan, C. S. Tan and R. Reif, “Microstructure evolution and abnormal grain growth during copper wafer bonding,” Applied Physics Letters, 81(20), pp 3774-3776, 2002.

[12] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, “Temperature and Duration Effect on Microstructure Evolution during Copper Wafer Bonding”, Journal of Electronic Materials, 32(12), pp 1371-1374, 2003.

[13] K. N. Chen, C. S. Tan, A. Fan and R. Reif, "Morphology and bond strength of copper wafer bonding", Electrochemical and Solid-State Letters, 7(1), pp G14- G16, 2004.

[14] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, “Contact Resistance Measurement of Bonded Copper Interconnects for Three-Dimensional Integration Technology”, IEEE Electron Devices Letters, 25(1), pp 10-12, 2004.

[15] Kuan-Neng Chen, Sang Hwui Lee, Paul S. Andry, Cornelia K. Tsang, Anna W. Topol, Yu-Ming Lin, JianQiang Lu, Albert M.Young, Meikei Ieong, and Wilfried Haensch, “Structure Design and Process Control for Cu Bonded Interconnects in 3D Integrated Circuits”, 2006 International Electron Devices Meeting (IEDM), pp. 367-370, San Francisco CA, Dec. 11-13, 2006.

[16] J. J. McMahon, J.-Q. Lu and R. J. Gutmann, "Wafer bonding of damascene-patterned metal/adhesive redistribution layers for via-first three-dimensional (3D) interconnect," Proceedings Electronic Components and Technology, 2005. ECTC '05., Lake Buena Vista, FL, USA, 2005, pp. 331-336 Vol. 1, doi: 10.1109/ECTC.2005.1441287.

[17] R.J. Gutmann, J.J. McMahon, S. Rao, F. Niklaus, and J.- Q. Lu, “Wafer-Level Via-First 3D Integration with Hybrid-Bonding of Cu/BCB Redistribution Layers”, Proceedings of International Wafer-Level Packaging Congress (IWLPC), pp. 122-127, SMTA, Nov. 2-4, 2005.

[18] R. R. Yu, F. Liu, R. J. Polastre, K.-N. Chen, X. H. Liu, L. Shi, E. D. Perfecto, N. R. Klymko, M. S. Chace, T. M. Shaw, D. Dimilia, E. R. Kinser, A. M. Young, S. Purushothaman, S. J. Koester and W. Haensch, “Reliability of a 300-mm-compatible 3DI technology based on hybrid Cu-adhesive wafer bonding”, 2009 Symposia on VLSI Technology and Circuits, Kyoto, Japan, Jun. 15-18, 2009.

[19] K. N. Chen, T. M. Shaw, C. Cabral, Jr., and G. Zuo, “Reliability and structural design of a wafer-level 3D integration scheme with W TSVs based on Cu-oxide hybrid wafer bonding”, 2010 International Electron Devices Meeting (IEDM), San Francisco CA, Dec. 6-8, 2010.

[20] Kuan-Neng Chen, Zheng Xu, and Jiang-Qiang Lu, “Electrical Performance and Alignment Investigation of Wafer-level Cu-oxide Hybrid Bonding,” IEEE Electron Device Letters, 32(8), pp. 1119-1121, Aug 2011.

[21] K.N. Chen, C.K. Tsang, A.W. Topol, S.H. Lee, B.K. Furman, D.L. Rath, J.-Q. Lu, A.M. Young, S. Purushothaman, and W. Haensch, “Improved Manufacturability of Cu Bond Pads and Implementation of Seal Design in 3D Integrated Circuits and Packages”, 23rd International VLSI Multilevel Interconnection (VMIC) Conference, Fremont CA, Sep.25-28, 2006.

[22] Y. Kagawa et al., "An Advanced CuCu Hybrid Bonding For Novel Stacked CMOS Image Sensor," 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, Japan, 2018, pp. 65-67, doi: 10.1109/EDTM.2018.8421453.

[23] B. Zhang et al., "Scaling Cu/SiCN Wafer-to-Wafer Hybrid Bonding down to 400 nm interconnect pitch," 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 2024, pp. 312- 318, doi: 10.1109/ECTC51529.2024.00058.

[24] Yan-Pin Huang, Yu-San Chien, Ruoh-Ning Tzeng, and Kuan-Neng Chen, “Demonstration and Electrical Performance of Cu–Cu Bonding at 150 °C With Pd Passivation,” IEEE Transactions on Electron Devices, 62(8), pp. 2587-2592, Aug. 2015.

[25] Zhong-Jie Hong, Demin Liu, Shu-Ting Hsieh, Han-Wen Hu, Ming-Wei Weng, Chih-I Cho, Jui-Han Liu, and Kuan-Neng Chen, “Room Temperature Cu-Cu Direct Bonding Using Wetting/Passivation Scheme for 3D Integration and Packaging,” 2022 Symposia on VLSI Technology and Circuits, Honolulu, HI, Jun. 12-17, 2022.

[26] Demin Liu, Po-Chi Chen, Chien-Kang Hsiung, Shin-Yi Huang, Yan-Pin Huang, Steven Verhaverbeke, Glen Mori, and Kuan-Neng Chen, “Low Temperature Cu/SiO2 Hybrid Bonding with Metal Passivation,” 2020 Symposia on VLSI Technology and Circuits, Virtual Conference, Jun. 14-19, 2020.