How can we help you? Get in touch with us

IC壽命試驗與ELFR

|

半導體元件壽命試驗與早夭失效率評估(IC OLT and ELFR Test) |

半導體產業是電子產業的火車頭,隨著製程技術不斷進步,以及使用者對於產品的品質要求,以 JEDEC 為首的國際組織,制定了多項基本參考規範,其中壽命試驗測試屬於半導體元件測試項目中最重要的一環。壽命測試相較於一般測試項目而言相對複雜,主要在於老化板(Burn-in Board)的設計與製作。

|

老化板 (Burn In Board) 設計製作 |

老化版的設計與製作是整個半導體壽命測試的關鍵,由於半導體元件之應用頻率、速度、發熱、阻抗匹配(Impedance)等考量,在老化板的設計考量上相對複雜。

閎康可靠度實驗室提供老化板設計製作一條龍服務,在考量成本下,根據產品規格可選擇適當之萬用板(Universal Board),製作轉板解決之;對於特殊規格,亦可協助客戶設計專用板進行測試。

圖1 萬用型老化板 |

圖2 LC2Socket 樣本圖 |

|

加速壽命試驗(Accelerated Lifetime Test) |

半導體元件加速壽命試驗,主要是透過溫度、電壓或電流等,對晶片(device)實際運作的壽命時間模擬。產品測試需要使用老化板(Burn-in board),測試溫度的考量需得考慮到使用者的環境以及晶片本身的結溫(Junction Temperature)進行設定。常見的加速壽命試驗如下述兩類:

1. 高溫壽命試驗(HTOL,High Temperature Operating Life Test)

測試目的是利用高溫及電壓加速測試,以評估晶片長時間的使用壽命,測試中加入的是動態訊號而非靜態偏壓,更貼近實際的產品使用狀態。

2. 早夭失效率試驗(ELFR,Early Life Failure Rate)

測試目的是利用高溫及電壓加速測試來找出早夭產品,進而評估產品的早夭比率,測試中加入的是動態訊號而非靜態偏壓。

|

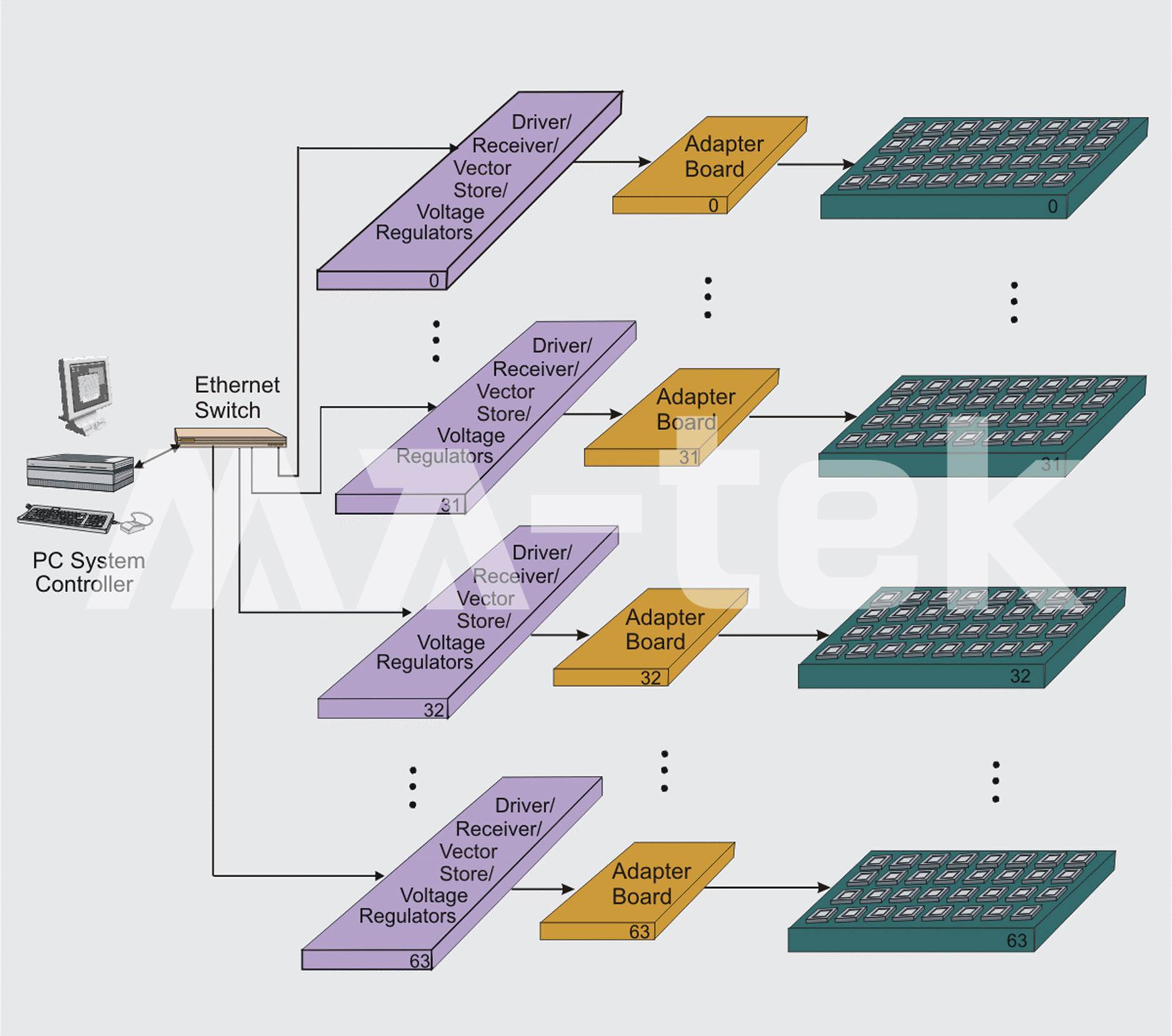

圖3 IC 加速壽命試驗架構圖

|

壽命與失效率預估(Lifetime and Failure Rate Prediction) |

以溫度為主要加速因子(Accelerated Factor,AF)之可靠度試驗,多以阿瑞尼亞氏方程式(Arrhenius’ Equation)的指數方程式為基礎,選擇適當的活化能(Activation Energy)估算加速度倍數差異,透過加速壽命試驗可以推估在特定的信心水準下的使用壽命。半導體元件多以 FIT (Failure In Time) 與 MTTF (Mean Time To Failure)兩者計算之。然而對於使用者而言,不論是 FIT 或者 MTTF,均不容易告訴客戶該元件未來所面臨的風險會有多高,反而造成誤解,且對於生產備料庫存管理造成困難。

另一個常用的壽命估算方式,有別於傳統 FIT 或 MTTF 模式,以使用需求時間(例如10年)除以加速因子來推算所需要的測試時間,車用電子即為典型的代表。閎康科技在晶片壽命試驗,由一群在半導體製程與設備具有多年經驗的專業人員所組成,提供客戶一條龍服務(One Stop Service),在台灣與上海實驗室均可提供壽命試驗服務,實驗室目前設備能力如下表,提供不同客戶個別的需求:

|

表1 元件老化測試機台規格

|